Taiwan Semiconductor Manufacturing Firm (TSMC) is acknowledged because the world chief in semiconductor fabrication. Although the firm is working with prime EDA firms to certify their IC design instruments for its 2 nm course of expertise, TSMC has already set its sights on 1.6 nm chips within the close to future.

TSMC is setting up two new factories to help future 2nm course of expertise. Picture (cropped) used courtesy of TSMC

Chip designers will need to have digital design automation (EDA) instruments to develop built-in circuits for these new nodes. To this finish, among the business’s most outstanding EDA firms, Synopsys, Cadence, and Siemens, every just lately introduced collaborations with TSMC so as to add help for TSMC’s newest nodes to their EDA device suite.

Cadence: A Push for 3D ICs, Superior Nodes, and Photonics

Cadence and TSMC just lately introduced a collaborative effort to optimize Cadence’s device suite for TSMC’s 2-nm course of applied sciences.

These optimizations cowl a variety of functions, from digital and analog design flows to semiconductor energy integrity evaluation. Cadence’s Innovus Implementation System and Genus Synthesis Answer are actually licensed for TSMC’s N2 design flows, and the Cadence Integrity 3D-IC platform now options enhanced capabilities for dealing with advanced multi-chip designs utilizing TSMC’s 3DFabric applied sciences.

Cadence’s Integrity 3D-IC platform. Picture used courtesy of Cadence

The collaboration additionally extends to customized or analog instruments optimized for TSMC’s N2 Course of Design Equipment (PDK), together with the Virtuoso Schematic Editor and the Virtuoso ADE Suite. These platforms help superior circuit simulation and optimization needed for high-performance and low-power semiconductor functions.

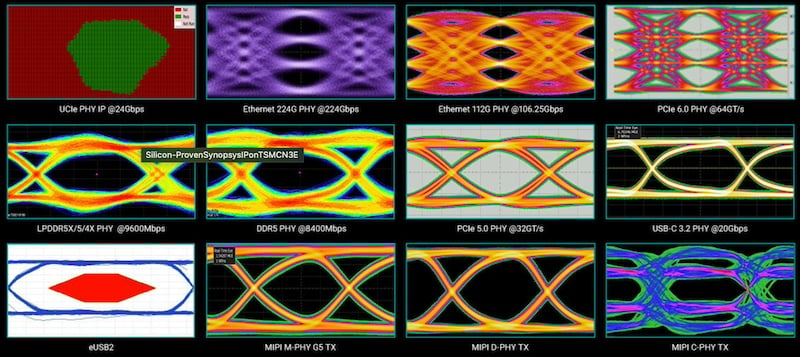

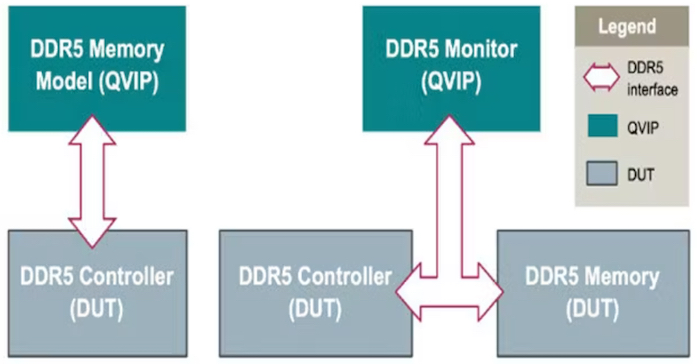

The partnership might advance photonic built-in circuit design, with new flows to help TSMC’s Compact Common Photonic Engine (COUPE) expertise. As a part of this, the businesses have launched a complete portfolio of IP cores optimized for TSMC’s N3 course of expertise, overlaying interfaces akin to UCIe, DDR5, LPDDR5, GDDR6, PCIe 5.0/CXL2.0, and PCIe 6.0/CXL3.0.

Synopsys: AI-Pushed Design Flows for N2

Synopsys can also be teaming up with TSMC to optimize the fab’s chip design processes utilizing synthetic intelligence and photonic built-in circuit (PIC) applied sciences.

TSMC is integrating the Synopsys.ai suite to facilitate environment friendly analog and digital design on its N3, N3P, and N2 course of applied sciences. This consists of the DSO.ai platform, which automates chip design and optimizes the tradeoff between energy, efficiency, and space traits in superior chip designs.

Synopsys IP on TSMC N3E. Picture used courtesy of Synopsys

The collaboration goals to develop built-in radio frequency (RF) and photonic design flows as nicely. With fashionable processing paradigms like multi-die integrations demanding sooner and extra environment friendly inter-chip communication, builders are turning to photonic design to attain greater information transmission charges with decrease latency. Synopsys will use TSMC’s COUPE expertise in its Photonic IC design and 3DIC Compiler toolsets to streamline the design and manufacturing course of of those photonic parts.

Synopsys additionally introduced enhancements to its IP choices for TSMC’s superior nodes. This features a broad array of Basis and Interface IPs like UCIe, HBM4/3e, and PCIe 7.x/6.x.

Siemens: IC Verification Instruments Licensed for N2

A number of Siemens EDA instruments have efficiently achieved certification with TSMC’s newest semiconductor processes, such because the superior N2 course of.

Key Siemens instruments that obtained certification embrace the Calibre nmPlatform device suite, which incorporates instruments like Calibre nmDRC for design rule checking, Calibre nmLVS for format vs. schematic verification, Calibre Sample Matching, and Calibre PERC. The certification of those instruments ensures they’ll help the TSMC N2 node, permitting for the design and manufacturing of smaller, extra environment friendly, and highly effective semiconductors.

Siemens’ Calibre 3DSTACK. Picture used courtesy of Siemens

Moreover, the Siemens Analog FastSPICE platform, recognized for its precision in verifying nanometer-scale analog, RF, mixed-signal, reminiscence, and customized digital circuits, has been licensed for TSMC’s N3P, N2, and N2P processes.

For 3D integration, Siemens’ Calibre 3DSTACK answer has been accepted to help TSMC’s 3Dblox commonplace. This commonplace is a tenet for 3D IC designs that allows refined thermal evaluation as a part of TSMC’s 3DFabric superior packaging applied sciences. It permits designers to foresee and mitigate potential overheating points in densely packed ICs, serving to preserve efficiency and reliability in dense superior nodes.

EDA for Subsequent-Gen Nodes

Designers want EDA instruments optimized for TSMC’s new course of nodes to completely leverage the expertise’s energy. By collaborating with TSMC, firms like Cadence, Synopsys, and Siemens are immediately integrating TSMC’s wealth of data into their device suite and offering IC designers with dependable instruments to design the following era of semiconductor merchandise.